ARMPIT SCHEME is an interpreter for the Scheme language (lexically-scoped dialect of Lisp) that runs on RISC microcontrollers with ARM core. It is based mostly on the description of the Revised^5 Report on the Algorithmic Language Scheme (r5rs) and is transitioning towards R7RS-small. It contains some extensions (for I/O) and some omissions (to fit within MCU memory). It is designed to support multitasking and multiprocessing (partially for now). Armpit Scheme is expected to be well suited to educational settings, including student projects in courses on control and instrumentation, or capstone design courses where microcontrollers are needed. It is meant to enrich the spectrum of interpreted languages available for MCUs (eg. BASIC and FORTH) and can be an alternative to MCU-based bytecode interpreters (eg. for Scheme, Java, Lua or Python) and to compiled languages (eg. C).

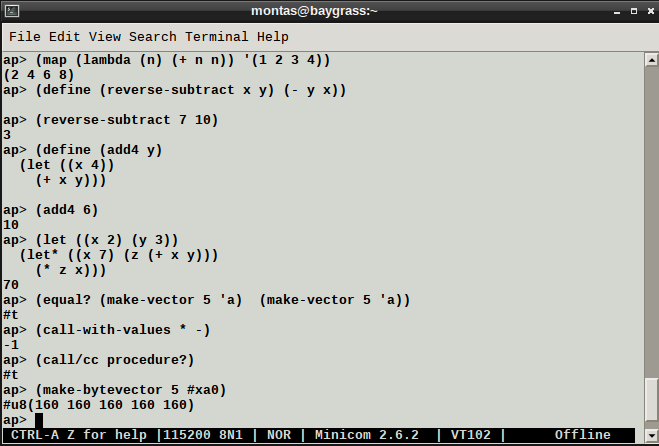

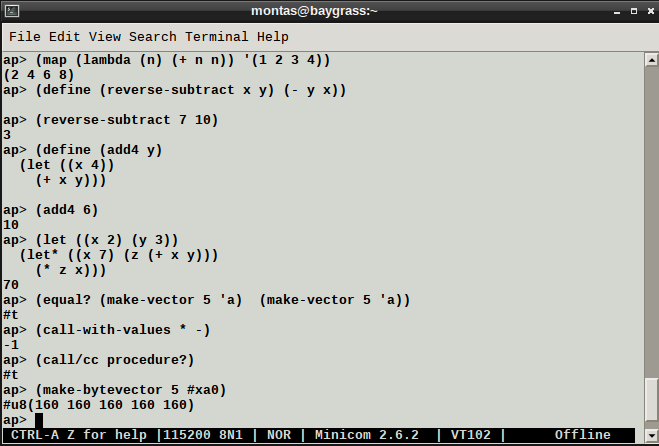

The name "Armpit" was selected for this project because it includes "ARM" (as in ARM core MCU) and "pit" (as in kernel, noyau, nucleus, the core of an Operating System (OS)). Armpit Scheme, once loaded, governs the operation of the MCU, and is "Scheme to the metal" in the sense of running without any other OS. It may be thought of as turning the MCU into a rudimentary Scheme machine. The screenshot below shows the system running on a NanoPC-T3 Plus, communicating via USB. Minicom is used to communicate with the board which reads, evaluates and prints the result of the entered expressions.

This version of Armpit Scheme supports USB keyboards for various MCU boards. The figure below shows a Logitech wireless USB keyboard used with the NanoPC-T3 Plus (in a metal case; right behind the keyboard).

External display, on LCD or via DVI or HDMI, is also supported for some of the boards. Connecting both a keyboard and an external display provides an environment that is nearly standalone. Still missing are an editor, mouse support (possibly), and the ability of the "boot.scm" startup file to properly instantiate libraries. The code needed to use keyboard and display is given in the example pages (below). Figure 3 shows the result of loading the console.scm file in a running system.

The latest development snapshot of Armpit Scheme is 080. It is distributed under the MIT License and is a beta releases, with both known bugs and unknown bugs. The source code, and pre-assembled (ready-to-use) binary image files, can be downloaded from the armpit project page at SourceForge. You can also view the source code from your web browser.

In version 080, the base characters are from the 16-bit unicode set (rather than 7-bit ASCII). Strings are made up of sequences of these characters, and symbols (eg. function names) are encoded in UTF-8. A memory allocation nursery is used on Cortex-M to help speed-up garbage collection in these slower systems. The code is split-up into a small Live-SD (LSD) bootloader which is MCU- (and board-) specific, and the Scheme interpreter (ArmPit Scheme, aka: APS) which depends on the MCU's Machine Language (Thumb2, Aarch32 or Aarch64) and allows for two Thumb2 memory layouts. The MCUs capable of 64-bit operation (eg. Cortex-A53) are run in 64-bit mode (not 32-bit compatibility mode). To produce a unified code base that successfully assembles and runs across the selected targets, some minimum requirements were set for the boards on which Armpit Scheme 080 runs (relative to previous versions). For 080, the MCU needs to be a Cortex-M4F or above, with a FPU, an MMU or MPU, and the board needs to have an SD-card slot for the LSD bootloader to fetch the APS. Wherever possible, the bootloader is also placed on an SD-card, to be loaded and executed by the MCU's boot ROM, such that the overall operation is as a Live-SD (or Live Disk) whereby the MCU (or board) flash storage is not needed (and not used). In all cases, user files are stored on the SD card.

The system is documented in several web pages:

The lastest release is designed to run on the following boards (see build_all script):

| CPU | USB | LCD / | USB (*) | |||||

| BOARD | MANUFACTURER | MCU | CORE | MHZ (*) | RAM | DEVICE | DVI (*) | KEYBOARD |

| EK-TM4C1294XL | TI | TM4C1294NCPDT | Cortex-M4F | 120 | 256 KB | Native | - | - |

| STM32F429 Discovery | ST | STM32F429ZIT6U | Cortex-M4F | 168 | 8 MB | Native | LCD | - |

| LPC4330-Xplorer | NGX Electronics | LPC4330 | Cortex-M4F | 204 | 128 KB | Native | - | - |

| LPC4357-Xplorer | NGX Electronics | LPC4357 | Cortex-M4F | 204 | 32 MB | Native | LCD | yes |

| STM32F746G Discovery | ST | STM32F746NGH6U | Cortex-M7 | 216 | 8 MB | Native | LCD | yes |

| SAMV71-Xplained-Ultra | Microchip | AT91SAMV71Q21A | Cortex-M7 | 252 | 2 MB | Native | - | - |

| SAME70-Xplained | Microchip | ATSAME70Q21 | Cortex-M7 | 300 | 2 MB | Native | - | - |

| MIMXRT1050 EVK | NXP | MIMXRT1052 | Cortex-M7 | 600 | 32 MB | Native | LCD | - |

| SAMA5D4-Xplained-Ultra | Microchip | ATSAMA5D44 | Cortex-A5 | 528 | 512 MB | Native | DVI | yes |

| BeagleBoard (B7) | TI | OMAP3530 | Cortex-A8 | 600 | 128 MB | Native | - | - |

| Overo Tide | Gumstix | OMAP3530 | Cortex-A8 | 720 | 512 MB | Native | - | - |

| BeagleBone Black | TI | AM3359 | Cortex-A8 | 900 | 512 MB | Native | DVI | yes |

| BeagleBoard-XM-(C2) | TI | DM3730 | Cortex-A8 | 1000 | 512 MB | Native | DVI | yes |

| Duovero Crystal | Gumstix | OMAP4430 | Cortex-A9 | 900 | 1 GB | Native | DVI | yes |

| Parallela P1601 Desktop | Adapteva | Xilinx XC7Z010 | Cortex-A9 | 667 | 1 GB | Native | - | - |

| A64-Olinuxino | Olimex | Allwinner A64 | Cortex-A53 | 672 | 1 GB | - | - | - |

| NanoPC-T3 | FriendlyARM | Samsung S5P6818 | Cortex-A53 | 800 | 1 GB | Native | DVI | yes |

| NanoPC-T3+ | FriendlyARM | Samsung S5P6818 | Cortex-A53 | 800 | 2 GB | Native | DVI | yes |

| iMX8M-EVK | NXP | i.MX8M | Cortex-A53 | 800 | 3 GB | uart conv. | - | - |

| Odroid-C2 | HardKernel | Amlogic S905 | Cortex-A53 | 1536 | 2 GB | Native | - | - |

(*) CPU speeds (MHz) are configured speeds and may be lower than the allowable maximum for any of the MCUs in the table. LCDs, DVI displays and USB keyboards are programmed from within user or library space (not in the core -- see mcu-specific program examples).

External links of potential interest include: